ITU-T 勧告G.726規格に準拠したFPGA向けADPCMトランスコーダIPの64チャネル対応版です。

PCMコーデックと組み合わせることで、ADPCMコーデックLSIと置き換えることが可能です。

特長

- ITU-T 勧告G.726準拠 32kbps ADPCM トランスコーダ

- μ-law / A-law 両対応

- 64チャネル対応

- メモリによる外部インタフェース

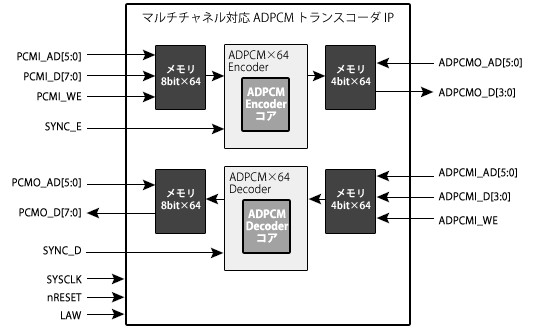

ブロック図

インタフェース

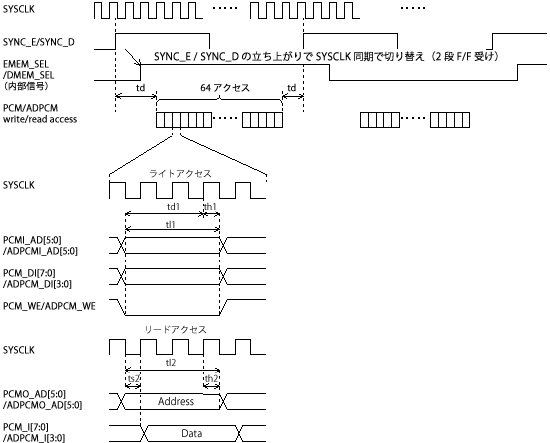

タイミングチャート

| 名称 | 値 |

|---|

| SYSCLK | min 1MHz max **Mhz (※) |

|---|

| td | SYSCLK の3T 以上 |

|---|

| tl1 / tl2 | 2 面メモリは何れもSYSCLK 信号をクロックとした同期メモリで構成されるため、アドレス、データ入力、WE 信号は最低でもSYSCLK の1T 期間アクティブにすること。 |

|---|

| ts1 / th1 | (※) |

|---|

| ts2 / th2 | (※) |

|---|

| (※)SYSCLK の最大周波数、セットアップ/ホールド時間(ts1/th1, ts2/th2)は、使用デバイス(スピードグレード)をご指定頂いた後に提示致します。 |

規模(参考)

| FPGAデバイス | ALTERA製 CycloneIII(EP3C10) |

|---|

| 使用LE数 | 約9,000LEs |

|---|

| メモリ使用量 | 9kbit メモリブロック20 個 |

|---|

| DSPブロック(乗算器)使用数 | 9×9bit乗算器20個 |

|---|

| ※ その他デバイスの対応に関してはお問い合わせください。 |

ご提供方法

- ご要望によりIP のカスタマイズおよび機能追加してのご提供も可能です。

- 外部制御回路等の周辺回路のカスタム設計も承りますので、ご相談ください。

- Verilog-HDL 言語で設計しています。(VHDL 言語での対応についてはご相談ください。

- マクロ(ネットリスト)によるご提供やROM 形式でのご提供も可能です。

お問い合わせ

この製品に関するお問い合わせはこちら

カタログのダウンロードはこちら

カタログのダウンロードはこちら

関連製品