# リードソロモン Encoder/Decoder

無線機器、×DSLモデム、デジタルTVなど幅広い分野で 通信品質を向上させる目的で使用されているリードソロモン符号 (RS符号)方式の誤り訂正符号 Encoder/Decoder コアです。

【仕様】 TYPE A、TYPE B 2種類の IP をご用意しております。

|       | TYPE A                                                | TYPE B                                             |  |

|-------|-------------------------------------------------------|----------------------------------------------------|--|

| 符号    | RS(255,239;8)                                         | RS(255,247;4)                                      |  |

| 原始多項式 | X^8 + X^4 + X^3 + X^2 + 1                             |                                                    |  |

| 生成多項式 | $G(X) = (X+1)(X+ )(X+ ^2) \cdot \cdot \cdot (X+ ^15)$ | $G(X) = (X + )(X + ^2) \cdot \cdot \cdot (X + ^8)$ |  |

| 遅延量   |                                                       |                                                    |  |

可変データブロック長に対応。

チェックビットの Byte 数や原始多項式・生成多項式は、 ご要望に応じてカスタマイズが可能。

ビット/バイトインターリーブ機能の追加も可能。

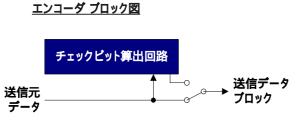

# 【ブロック図】

例)送信側で元データ239byteにエンコーダで 算出したチェックビット16byteを付加して 255byteのデータブロックを構成して送信 した場合

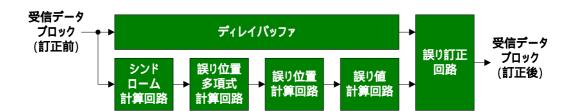

受信側デコーダでは255byte中8byteまで のエラーを検出し訂正することが可能に かります

デコーダ ブロック図

## 【外部インタフェース】

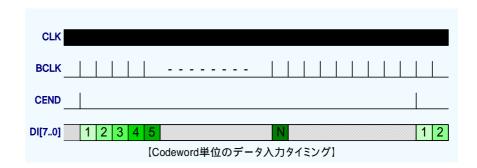

### 1. エンコーダ

| 信号名    | I/O | 機能                          |

|--------|-----|-----------------------------|

| nRESET | I   | FECリセット信号<br>(負論理パワーオンリセット) |

| FECENB | I   | FEC動作イネーブル信号                |

| CLK    | ı   | ビット同期クロック                   |

| BCLK   | 1   | バイト同期クロック                   |

| CEND   | ı   | FECコードワード終了信号               |

| DI[70] | Ī   | 入力データ                       |

| DO[70] | 0   | 出力データ                       |

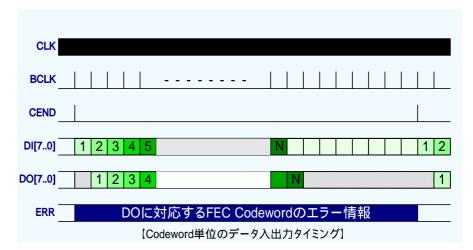

#### 2. デコーダ

| 信号名     | I/O | 機能                                                       |

|---------|-----|----------------------------------------------------------|

| nRESET  | I   | FECリセット信号<br>(負論理パワーオンリセット)                              |

| FECENB  | -   | FEC動作イネーブル信号                                             |

| CLK     | - 1 | ビット同期クロック                                                |

| BCLK    | -   | バイト同期クロック                                                |

| CEND    | -   | FECコードワード終了信号                                            |

| DI[70]  | -   | 入力データ                                                    |

| DO[70]  | 0   | 出力データ                                                    |

| ERR[10] | 0   | 受信データエラー情報<br>OX:エラーなし<br>10:修復可能なエラー発生<br>11:訂正不可能エラー発生 |

制御信号は FECENB、BCLK、CEND のみで単純な構成 FECENB 端子を使うことによってパースト的なデータに対応可能

【規模と速度(参考)】 TYPE B の例

デバイス: ALTERA 製 Cyclone (EP1C3)

使用 LE 数 : 約 1,900LEs (エンコーダ部:約 200LEs / デーコーダ部:約 1700LEs)

必要 Memory 空間 : 8kbit (デコーダのみ使用)

最大動作速度 : 120MHz

【記述言語】 Verilog-HDL ( VHDL での対応も可能です。詳細はお問合せください。)

ご要望により IP のカスタマイズおよび機能追加してのご提供も可能です。 外部制御回路等の周辺回路のカスタム設計も承りますので、ご相談〈ださい。 HDL 言語で設計していますので、様々な FPGA や ASIC デバイスへ対応出来ます。 マクロ(ネットリスト)によるご提供や ROM 形式でのご提供も可能です。

<u>通信機器・画像処理関連ハードウェア、ファームウェアの</u> 受託開発も承ります。

# 株式会社テクノクリエート

【本社】〒980-0801 仙台市青葉区木町通1 - 8 - 28 武山興産ビル 【東京技術センター】〒206-0014 東京都多摩市乞田1284永山 U ビル

#### お問い合わせはこちら

© 0120-733-606(お問い合わせセンター) E-mail:info@techno-create.com http://www.techno-create.com