MPSC PLD(シリアルコントローラ)

本製品は、NEC製μPD72001互換を目指したマルチ・プロトコル・シリアル・コントローラ(MPSC)のFPGA用IPコアです。

本IPはuPD72001同様、調歩同期、COP、BOPの3種のプロトコルをサポートしています。

ルネサス エレクトロニクス株式会社様のWebサイトにて本製品へのリンクが掲載されています。

特長

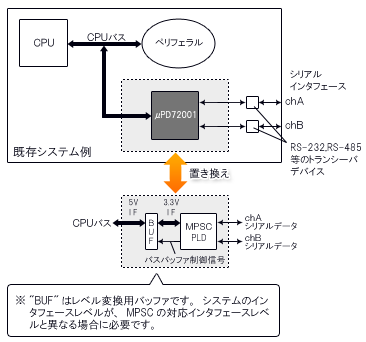

- NEC製μPD72001を使用しているシステムに制御ソフトウェアを大幅に変更せずに置き換えることが可能です。

- RTL(VHDL)もしくはFPGA用ROMデータにてご提供致します。

- 必要なプロトコルおよびチャネル数のみに限定し、より小規模なFPGAに実装することも可能です。(カスタマイズ対応になります)

- 5Vインタフェース対応機能(レベル変換用外部バスバッファ制御機能)搭載。

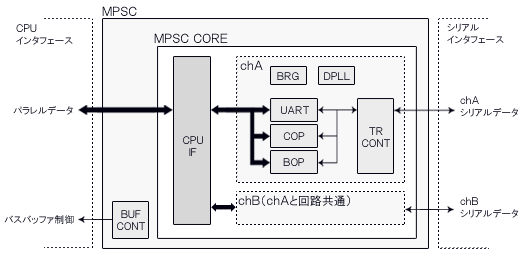

構成

| CPU IF | CPUインタフェースブロック | BRG | ボーレートジェネレータ |

|---|---|---|---|

| UART | 調歩同期プロトコルエンジン | DPLL | ディジタル・フェーズ・ロックド・ループ |

| COP | COPプロトコルエンジン | TR CONT | シリアル送受信制御ブロック |

| BOP | BOPプロトコルエンジン | BUF CONT | 外部バスバッファ制御回路 |

各プロトコルエンジンはそれぞれ独立に2ch分搭載されているため、例えば一方のチャネルをCOPで送受信、もう一方のチャネルをBOP で送受信というような利用が可能です。

置き換え例

規模と性能

| FPGAデバイス | ALTERA 製CycloneIII(EP1C6) |

|---|---|

| 使用LE数 | 約3,000LEs |

| メモリ使用量 | 0 |

| 最大動作速度 fMAX | 50MHz |

| ※ その他デバイスの対応に関してはお問い合わせください。 | |

μPD72001との機能相違点

| ○:対応機能 / ×:未対応機能 / △:対応機能(一部相違) | ||||

| ブロック | 機能 | uPD72001 | MPSC PLD | |

|---|---|---|---|---|

| 全体 | データフォーマット | NRZ | ○ | ○ |

| NRZI | ○ | ○ | ||

| FM0 | ○ | × | ||

| FM1 | ○ | × | ||

| マンチェスタ | ○ | × | ||

| 自己折り返しテスト機能 | ○ | × | ||

| 水晶発信回路 | ○ | × | ||

| スタンバイ機能 | ○ | × | ||

| 外部トランシーバ制御機能 | × | ○ | ||

| COP | モード | Mono-sync | ○ | ○ |

| Bi-sync | ○ | ○ | ||

| External-sync | ○ | × | ||

| キャラクタビット長設定 | ○ | ×(8bit固定) | ||

| パリティチェック機能 | ○ | × | ||

| 生成多項式 | CRC-CCITT | ○ | ○ | |

| CRC-16 | ○ | × | ||

| BOP | SDLC LOOPモード | ○ | ○(専用バージョン) | |

| フラグ設定 | ○ | ×(0x7E固定) | ||

| 受信データ長設定 | ○ | ×(8bit固定) | ||

| Residueコード | ○ | △(コード値に相違あり) | ||

| ||||

ご提供方法

- ご要望によりIP のカスタマイズおよび機能追加してのご提供も可能です。

- 外部制御回路等の周辺回路のカスタム設計も承りますので、ご相談ください。

- マクロ(ネットリスト)によるご提供やROM 形式でのご提供も可能です。

- 評価用モジュールも貸し出ししております。※詳細はお問い合わせください。